# Fondamenti di Elettronica – Ing. INFORMATICA - AA 2014/2015

## Prova in itinere del 6 Maggio 2015

# Indicare chiaramente la domanda a cui si sta rispondendo. Ad esempio A1) ...

### Esercizio A

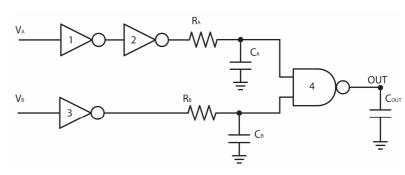

Si consideri il circuito digitale alimentato tra 0V e  $V_{DD}$ =3.3 V rappresentato in figura.

Dati:

$\begin{array}{lll} R_A{=}10k\Omega, & R_B{=}15k\Omega, & C_A{=}10pF, & C_B{=}15pF, \\ C_{OUT}{=}50pF & \end{array}$

Tutti i transistor, uguali tra loro, hanno le seguenti caratteristiche:

$K_{N}\!=1mA/V^{2}\,\text{, }|K_{P}|\!\!=\!\!0.5mA/V^{2}\,\text{; }V_{t,N}\!\!=\!\!|V_{t,P}|\!\!=\!\!0.5V.$

Tutte le porte logiche sono realizzate con il numero minimo di transistor.

- 1) Calcolare la soglia logica delle porte NOT (1,2,3).

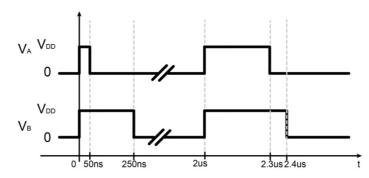

- 2) Considerando tutte le porte logiche ideali (ritardo nullo) e la NAND con soglia logica pari a  $V_{DD}/2$ , disegnare su un grafico quotato la forma d'onda dell'uscita quando i segnali  $V_A$  e  $V_B$  sono quelli riportati in figura:

- 3) Calcolare il tempo di propagazione (0-50%) dell'uscita quando agli ingressi della porta NAND sono applicati due generatori ideali di tensione che commutano entrambi istantaneamente da 0 a  $V_{DD}$ .

- 4) Determinare la potenza dinamica dissipata dal circuito con  $V_A$  onda quadra a frequenza 1MHz e duty cycle 20% e  $V_B$  onda quadra a frequenza 1MHz e duty cycle 50%. (Nota: considerare i fronti di salita dei due segnali sincroni).

#### Esercizio B

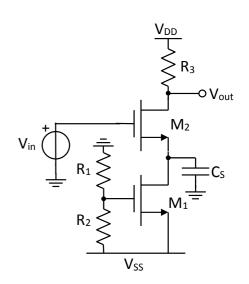

Si consideri l'amplificatore di piccolo segnale riportato in figura.

Dati:

$k_{M1}=1 \text{ mA/V}^2$ ,  $k_{M2}=4 \text{ mA/V}^2$ ,  $V_{T1}=V_{T2}=0.8 \text{ V}$

- $$\begin{split} &V_{\text{DD}}\!\!=\!\!+10V,\,V_{\text{SS}}\!\!=\!\!-10V\\ &R1\!=\!820k\Omega,\,R2\!\!=\!\!180k\Omega,\,R3\!\!=\!\!7k\Omega\\ &C_{\text{S}}\!\!=\!\!1\mu F \end{split}$$

- 1) Determinare la polarizzazione del circuito specificando la tensione di ogni nodo e il regime di funzionamento dei due transistori.

- 2) Calcolare il guadagno di piccolo segnale  $v_{out}/v_{in}$  a bassa frequenza ( $C_S$  aperto) e ad alta frequenza ( $C_S$  corto circuito).

- 3) Tracciare l'andamento temporale della tensione  $V_{out}(t)$  in risposta a uno scalino di tensione  $v_{in}(t)$  di ampiezza 1 mV.

- 4) Determinare l'intervallo di tensioni v<sub>in</sub>(t) (a bassa frequenza, ossia con C<sub>S</sub> assimilabile a un circuito aperto) applicabile al circuito senza modificare il regime di funzionamento dei transistori rispetto alla condizione di polarizzazione.

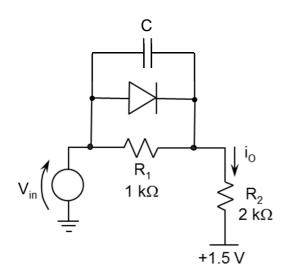

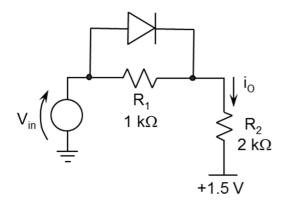

### Esercizio C

Si consideri il circuito in figura. Il diodo ha tensione di accensione  $V\gamma=0.7$  V.

- 1) Disegnare la transcaratteristica corrente di uscita ( $i_o$ ) in funzione della tensione di ingresso ( $V_{in}$ ) calcolandone tutti i punti significativi quando Vin varia nell'intervallo [-12V, +12V].

- 2) Disegnare l'andamento temporale di  $i_o(t)$  quando  $V_{in}(t) = 12V \cdot \sin(2\pi \ 1 \text{kHz}\ t)$  quotando tutti i punti significativi. Determinare la condizione sulla tensione di breakdown del diodo affinche' non entri mai in zona di breakdown con la  $V_{in}(t)$  data.

- 3) Si assuma ora che il diodo abbia la tensione di breakdown  $V_B$ =-3 V. Disegnare l'andamento temporale della potenza dissipata dal diodo con la medesima  $V_{in}$  data al punto precedente.

- 4) Si consideri una capacita' C=1 nF in parallelo al diodo come riportato nella figura seguente. Si calcoli l'andamento di  $i_o(t)$  in risposta ad un gradino di tensione della tensione di ingresso  $V_{in}$  da 0 a 5 V (si assuma che, prima della transizione, il circuito sia a regime nella condizione  $V_{in}=0$ ).